将异质结构导入先进的芯片导线(interconnect)深具发展潜力,不同导体材料之间的接口更扮演了关键角色,但目前在整合技术上仍面临了一些挑战。因此IMEC在2021年IEEE国际芯片导线技术会议(International Interconnect Technology Conference)上提出了几种可用来延续后段制程微缩的异质整合方法。

推进芯片的后段制程技术

芯片开发商现在正持续推动前段制程的晶体管发展,但同时,后段制程的内连导线技术却面临了开发挑战,难以跟进。

后段制程的处理步骤依照不同的金属层进行安排,包含局部导线层、中间导线层、半全局和全局导线层,这些金属层之间透过通孔(via)结构互连,通孔则以金属填充。然而,每一代新制程技术所面临的布线拥塞和讯号严重延迟的问题变得越来越棘手,迫使芯片开发商必须为导线制程着想,考虑全新的整合方案和材料。

就现阶段进入量产的最先进5纳米制程来说,在关键的局部导线层,金属导线间距最短为28纳米。铜双镶嵌结构依然是导线制程中最费工耗时的步骤,但随着未来金属导线间距将微缩至21纳米以下,芯片开发商可能会逐渐淡出主流技术市场。像是IMEC就提出了一些替代的整合方案,包含通孔混合异质金属布线、半镶嵌制程,以及信道高度的零通孔结构,为往后的技术节点做好准备。

同时,其他质量因素(figure of merit)较高的导体材料也被纳入研究范围,用于前述的那些先进制程。这里说的质量因素,指的是块材电阻(bulk resistivity)与金属内部载子平均自由路径的乘积。目前备受瞩目的材料包含钴(Co)、钌(Ru)、钨(W),还有铝镍合金(AlNi)或钌钒合金(RuV3)等有序二元介金属化合物。

除此之外,研究人员也在密切关注石墨烯(graphene)的发展潜力,因为它具备优异的材料特性,现在正逐步进军(生物)感测、储能、光伏、光电和CMOS微缩等市场焦点应用。

为什么选用石墨烯?

近年来,石墨烯一直是芯片导线应用的研究重点,因为它具备发挥多种功能的发展潜力。例如,它常被当作金属材料的氧化阻障层和超薄扩散阻障层。研究人员也在评估利用多层石墨烯导线或纳米带(nanoribbon)当作替代导体的可行性。

石墨烯会在导线应用备受瞩目完全在意料之中,它具备高达200,000cm2V-1s-1的本质载子迁移率,还有108A/cm2的最高载流量。而且石墨烯的导热性佳,抗迁移韧性也具备竞争优势,还能制造出单层原子的结构,减薄组件层厚度,进而减缓RC延迟的问题。

图一 : 碳基材料与其他导线材料的特性比较表。碳基材料包含纳米碳管(carbon nanotube;CNT)、单层石墨烯(single layer graphene;SLG)和寡层石墨烯(few layer graphene;FLG);其他受到关注的金属材料则有钨、铜和钌。

尽管石墨烯具备这些吸睛的材料特性,但却有一大缺点:它不能用来当作局部导线层,因为本身的载流子数量不够。载流子不足会严重折损导电性,但导电性却是导线性能的关键指针,与迁移率和载子浓度成比例。所以经过建模证实,如果要用于(局部)导线层,就需要在例如铜等金属混杂好几层石墨烯,至于层数多寡,则必须考虑对电阻和电容的整体影响后做出取舍。

幸运的是,我们可以利用一些方法来调变石墨烯的传导性。有关「石墨烯纳米带」的研究—也就是窄带状图形化的石墨烯层,因此蔚为风潮。另一个改良方法则从石墨烯层和下方组件层之间的角方向着手。最后,我们还能透过掺杂(doping)来增强石墨烯的导电性,如此一来,石墨烯就有更多的电子和电洞来带动电流。

掺杂能以几种方式进行,例如金属诱发技术利用石墨烯和铜、钌等金属的直接接触来产生结晶。这些混合了金属和石墨烯的掺杂方法可以整合两种材料各自的最大优势:金属的高载子密度与石墨烯的高迁移率。

本文探讨在2纳米以下的芯片导线中采用金属/石墨烯混合结构的可行性。目前有两种结构正在进行研究,包括具备石墨烯覆盖层的金属组件,以及具备金属覆盖层的石墨烯组件。本研究锁定钌金属,业界近期逐渐把它当作取代铜的金属布线材料,但这里提到的概念未来应该可以延伸到其他的导线金属材料上。

采用钌覆盖层的石墨烯

本研究中,IMEC团队将化学气相沉积(CVD)的多层石墨烯薄膜,转移到物理气相沉积(PVD)的钌金属薄膜(通常是5纳米)上面,最终制成混合了钌和石墨烯的组件结构。结果发现,石墨烯在转移之后可以完整附着在大面积的钌金属薄膜上。

在导线应用,石墨烯的金属诱发掺杂技术获得了市场关注,预计会让石墨烯在与钌接触的接口产生结晶。为了了解并控制掺杂的结果,我们针对钌与石墨烯接触接口的电荷转移展开系统性研究。

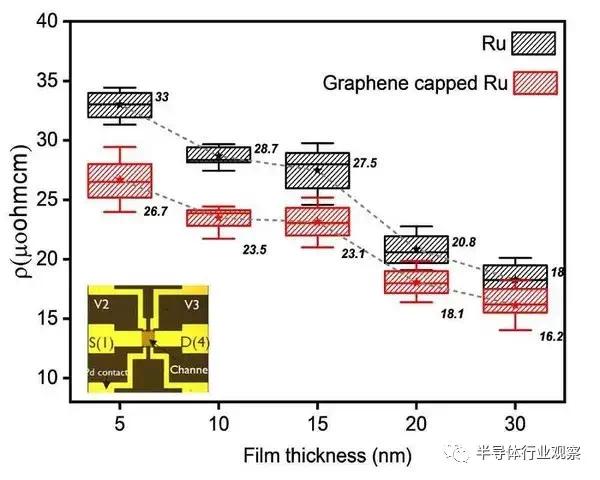

结果有两大发现:首先,研究人员发现钌在与石墨烯完成封装之后,薄膜电阻(sheet resistance)平均下降了15%。第二,他们发现石墨烯的费米能阶下降,价带比纯石墨烯低了约0.5eV,相当于1.9E13cm-2的电洞浓度。这项发现指出,在界面发生的金属诱发掺杂现象,让石墨烯在作为钌金属的覆盖层时,会变成P型。

经过本研究就可以确定钌在与石墨烯混合封装后,确实可以增加其作为导线的电气性能。不过,覆盖层内的导电机制究竟如何运作,还需要更多基础研究来提供见解。不论是将钌当作主要导体,辅以石墨烯来抑制金属内的散射机制,进而降低电阻,或是让这两种导体共同运作,其中,石墨烯会因为电荷迁移而具备比纯石墨烯还要高的导电性,这些混合方法现在都还在透过建立模型来取得更深入的了解。

此外,值得注意的是,钌金属导线在与石墨烯封装后,对温度变化的敏感度也降低了,这可能源于石墨烯的高导热性,散热机制因为多了额外或替代的传导路径而变得更有效率。这项发现也在开发未来的导线应用时引起关注,因为高度微缩的IC布线本身就会产生热能,其周围的介电组件散热能力又不足,导致芯片内部导线的热可靠度(thermal reliability)下降。

整体而言研究人员下了个结论,那就是采用石墨烯覆盖层的混合金属结构提供了一套解决导线RC延迟的解决办法。IMEC预期,这项技术未来能导入1纳米以下技术节点的后段制程。

金属与石墨烯混合的夹层结构

长远来看,IMEC团队为了进一步提升导电性,目前正在研究石墨烯与金属相互交替的堆栈结构。以类似三明治的方式堆栈出金属/石墨烯/金属…的夹层结构时,就会有第二个、第三个…的不同接口,每个都发挥同等重要的作用,都是在石墨烯上方沉积金属层时的接触接口。就像先前提到的研究结果,石墨烯和金属在接触接口自产产生的交互作用,能够改变石墨烯的物理特性,而且电子能带结构会因接口上的电荷分布而产生明显变化。

不过,设计石墨烯和金属接口是一项巨大挑战。通常(经过转移的)石墨烯层含有大量的非定向晶粒,这些晶界会充当线缺陷和上层表面金属沉积的晶粒成核中心位置。运用PVD或原子层沉积(ALD)等传统方法时,要让金属均匀覆盖在整片石墨烯基面上会有困难。而且石墨烯在转移后表面会受到杂质污染,所以需要采用合适的清洗方法,才不会损及石墨烯层。

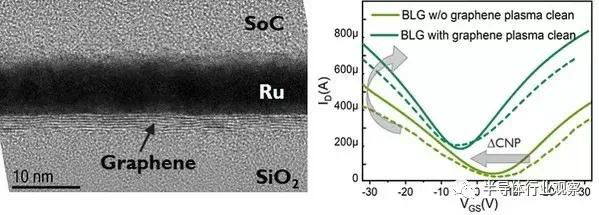

在一项实验室研究中,IMEC使用了氢气电浆(氩气/氢气顺流式电浆)来清洗石墨烯表面,然后利用电子束表面蒸镀的方式沉积金属(例如钌)。接着研究这些制程对石墨烯和钌堆栈的导电度产生了哪些影响。研究人员发现,石墨烯在接触氢气电浆后会产生N型掺杂,载流子浓度也会上升。不幸的是,单层石墨烯还是要面临电浆诱发的缺陷问题。在这些情况下,采用(经电浆清洗的)钌覆盖层的石墨烯组件,整体导电性提升了18%。这些初次研究成果相当振奋人心,预计未来还能透过调整氢气电浆的化学特性和清洗条件,以及增加交替层数,实现进一步的改良。

图三 : (图左)具备钌覆盖层并以电浆清洗的寡层石墨烯,此为电子穿透显微镜(TEM)影像;(图右)双层石墨烯组件的转移特性曲线,显示了经电浆清洗且转移后的石墨烯,在清洗步骤后开启电流时的变化,以及其电荷中性点的变动。实线和虚线分别代表从63个组件测得的转移曲线上限和下限。

迈向产业应用

上述研究成果展示了金属/石墨烯混合结构用于先进芯片导线的性能潜力,不过在导入12吋晶圆厂以前,这些导线制程都必须先克服在整合方面的挑战。举例来说,在本研究探讨石墨烯转移时,比较“精练”的沉积方法是让石墨烯直接成长在金属模板上,但是高质量石墨烯的成长温度高达900℃~1000℃,所以石墨烯生成不能用在一般导线会选用的金属材料上。已有研究展示在较低温的环境下进行沉积,但会导致缺陷和石墨烯质量的下降。

本研究采用的另一种替代方法牵涉到高质量石墨烯的移转,晶粒生成会先在白金箔上以CVD制程进行。这种转移方法在热预算受限时可能派得上用场。IMEC先前展示过如何在12吋晶圆上完成高质量石墨烯的分层和转移,但这些步骤可能会因为下方金属层表面平坦化的程度不同而面临考验。此外,石墨烯的移转势必增加好几道额外的处理步骤,还必须优化均匀度和制程控制。

为了将这些石墨烯和金属的混合架构导入产业应用,未来研究还必须加强对石墨烯层的缺陷和晶粒取向控制。

结语

对1纳米以下的节点来说,石墨烯和金属的混合结构有望成功延续后段制程的技术进展。本文探讨两种可能的混合架构,其中,石墨烯和金属之间的接口在导线整体的电性表现上都扮演了要角。尽管具备石墨烯覆盖层的金属导线技术较为成熟,但长远来看,交替层堆栈结构可能会被逐渐扩大采用。

来源:半导体行业观察